The Cores behind the core-dump

Why we core dump and the beginning of SRAM

This schema was taken from ed-thelen.org.

Thelen also gives a more detailed description including the hysteresis of the cores.

This schema was taken from ed-thelen.org.

Thelen also gives a more detailed description including the hysteresis of the cores.

The term dates back to an old type of memory, based on transformer cores. Saving the complete state of the system, “dumping”, the contents of these cores to e.g. a file; hence “core dump”.

Working principle:

The cores are ferite rings (toroids), similar to those used for transformers. Depending on their usage the rings are magnetisable to enable read and write operations for random access memory (RAM), read only memory (ROM) used the same rings. Although the technique to do a readout of the two memory systems differ, both systems use a magnetised ring as a binary 1. Both systems arrange their cores in a lattice, that use for each row and column a wire. To activate a core, on both corresponding wires, half the activation voltage is applied, so the needed magnetic field is generated at the position both wires intersect.

Usage as RAM:

This type of memory was used as RAM in the period 1955 till the late 70s. For a small graphical simulator visit the national mag lab, for another description have a look at the wiki page, which sadly has not that many sources. Although the contents of the memory are persistent, (non-volatile, static, static random access memory (SRAM)), the read was destructive. To read, a write signal was applied. If the core was already set, the output of the read signal will look differently then if the core had state binary 0. Core memory was more reliable and more radiation hardy compared to the early transistor RAM, so much so, that the flight computer memory of the space shuttles, was still implemented in core memory!

There was another system that worked on a similar principle, BIAX memory short for biaxial ferrite core.

Taken from computerhistory.org

Taken from computerhistory.org

Using 2 holes perpendicular to each other, a non-destructive readout is possible, with lower energy and faster response times, keeping its static property. According to The Free Dictionary which cites in turn the ‘Great Soviet Encyclopedia, 3. Edition’ - (Vizun, Iu. I. O primenenii elementov tipa “Biaks” ν operativnoi pamiati. Moscow, 1965), they were cheap to produce in scale. This however contradicts Computer History. They state that, although superior to the standard toroids in terms of their characteristics, the prohibitive price made them only practical in military applications.

Usage as ROM:

There are two configurations of the ROM. They both share the way for encoding 1s and zeroes, passing trough a core was high, not passing through a core meant low. Both ROMs where word adressable. This means that for each bit, a sense line was active and for each word a read line.

- Active reset - The same way as the RAM. This can be seen in the Apollo documentary below.

Altough with a much higher data rate per core. As several sense lines are passed through each core. Also, the cores need to be reset after a read.

Apollo´s active reset memory, taken from wikipedia.

Apollo´s active reset memory, taken from wikipedia.

- Passive reset, also named rope memory - Instead of a lattice, the cores are aranged in a line. And the each core has an individual sense line.

This method uses much weaker currents, so the cores reset them selfes after the selection current was shut off. The name comes from the rope assembly of cores and wires.

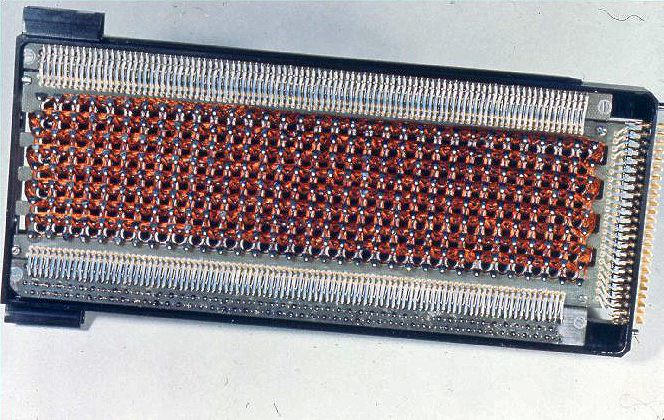

Rope memory prototype of the apollo memory. (according to Ken Shirriff's blog)

Rope memory prototype of the apollo memory. (according to Ken Shirriff's blog)

Rope memory of an ES EVM computer.

Picture from robotrontechnik.de

a german language site dedicated to the history of the GDR's biggest computer company, Robotron.

The line in green shows how the rope is placed on the pcb.

</figure>

</center>

Rope memory of an ES EVM computer.

Picture from robotrontechnik.de

a german language site dedicated to the history of the GDR's biggest computer company, Robotron.

The line in green shows how the rope is placed on the pcb.

</figure>

</center>

For unknown reasons, NASA moved away from the traditional way and used for the apollo guidance computer the active reset configuration. You can read about the core memory of an apollo guidance computer and its restoration at Ken Shirriff’s blog. Nasa used the passive configuration for prototyping and testing, according to Ken.

The east germanan company “Robotron” used for their ROM the traditional passive configuration.

Core rope memory schema, taken from robotrontechnik.de

Core rope memory schema, taken from robotrontechnik.de

Intrested in tinkering with the concepts yourself? There are several sites that give a step by step guide:

I think it is not proper to end this post without giving the clichéd size comparision: